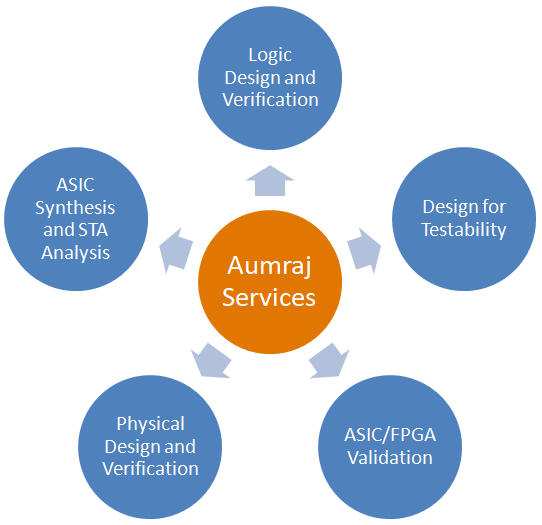

Logic Design and Verification

ASIC Synthesis and STA Analysis

Design for Testability (DFT)

Physical Design and Verification (RTL to GDSII)

ASIC/FPGA Validation

Logic Design and Verification

- Architecture definition/partition and RTL coding in Verilog.

- Verification using the latest tools such as VCS, Modelsim,Questasim etc.

- IP integration and verification using industry standard bus interfaces.

- Verification and integration of industry standard IP such as PCI Express(PCIE), USB, SATA, MIPI, Display Port, HDMI, etc.

- Expertise in next generation ARM based SoCs.

- Creation and verification of Bus Functional Models.

- Formal verification and assertion based verification.

ASIC Synthesis and STA Analysis

- Timing closure using the industry standard synthesis tools.

- Static timing analysis to avoid any violations after the synthesis.

- Scripting using tcl language and creating a synthesis environment.

- Work with physical synthesis tools to reduce the close the timing much faster.

- Offer smooth migration to industry standard physical design tools.

Design for Testability (DFT)

- Scan insertion using full, parallel, and partial scan methodology.

- BIST controller for testing the embedded memory blocks.

- JTAG controller for debugging the boundaries and for debugging the software.

- ATPG vectors generation for testing the manufacturing defects.

Physical Design and Verification (RTL to GDSII)

- Physical synthesis and Floor planning.

- DRC and LVS to check integrity of the design.

- Clock skew management and signal integrity issues.

- Timing closure and post-layout simulation.

- Verifying sub-nano physical design issues.

- Get the chip ready for tape out to the foundry.

- Tools: Magma, Cadence, Synopsis.

ASIC/FPGA Validation

- ASIC/FPGA chip Bring Up in lab.

- Board level silicon validation & debugging.

- Firmware development & debugging.

- High speed design.

- Expert in Altera & Xilinx FPGA flow.